Flash驱动控制--芯片擦除(SPI协议)

扫描二维码随身看资讯

使用手机 二维码应用 扫描右侧二维码,您可以

1. 在手机上细细品读~

2. 分享给您的微信好友或朋友圈~

摘要: 本篇博客具体包括SPI协议的基本原理、模式选择以及时序逻辑要求,采用FPGA(EPCE4),通过SPI通信协议,对flash(W25Q16BV)存储的固化程序进行芯片擦除操作。

关键词: SPI;Verilog HDL;Flash

【SPI协议通信模式】

SPI是Motorola公司推出的一种同步串行接口,是一种 高速、全双工、同步 的通信总线,广泛应用于存储器,数模转换器,实时时钟等。

- 优点:支持全双工通信,通讯方式简单,相对数据传输速率较快。

- 缺点:没有指定的流控制,没有应答机制,数据可靠性上存在缺陷。

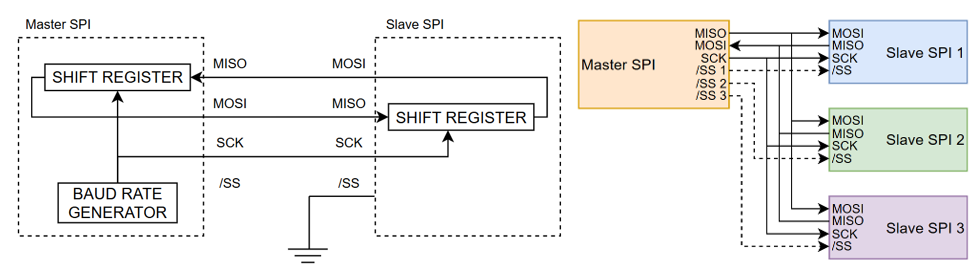

SPI协议通过四根线进行数据传输,即SCK(Serial Clock)、MOSI(Master Output Slave Input)、MISO(Master Input Slave Output)、/SS(Slave Select,低电平有效)(或/CS)。

接口处理方式: 一主一从(左)、一主多从【星型链式】(右)SPI通信要求主机和从机具有同步的时钟信号,传输速率直接受到时钟频率(SCLK)的影响。

信号线说明:

MOSI、MISO数据在SCK同步信号下传输,每个时钟周期传输一位数据,输入输出同步进行,要保证MSB或LSB先行需一致。/SS从设备信号选择线,由高变低,是SPI通讯的起始信号。当从设备/SS线检测到起始信号后,即为选中使能与主机通讯。/SS信号由低变高,为停止信号,从设备的选中状态被取消。

注:SPI每次数据传输可以8位或16位为单位,每次传输的单位数不受限制。

SPI通信时钟模式:

SPI通信加入了 时钟相位(CPHA) 和 时钟极性(CPOL) 的设置,通过组合CPOL和CPHA的不同设置,SPI共支持四种常见的时钟配置模式。

| CPOL | CPHA |

|---|---|

| 时钟极性,定义时钟信号在空闲状态下的电平 | 时钟相位,定义数据采样和转换的时钟边沿 |

| CPOL=0:SCK空闲为低电平 | CPHA=0:SCK的第一个边沿采样数据并转换输出信号 |

| CPOL=1:SCK空闲为高电平 | CPHA=1:SCK的第二个边沿采样数据并转换输出信号 |

在CPHA指示为l时, 数据就会在SCLK的第二个有效边沿被采样(/SS拉低后,空闲为高,为上升沿;空闲为低,下降沿),同时被锁存到寄存器中;如果CPHA 清零,数据就会在SCLK的第一个有效边沿被采样(/SS拉低后,空闲为高,为下降沿;空闲为低,为上升沿),同时被锁存起来。SPI的主从设备须配置相同的时序模式,见下图。

【W25Q16BV操作说明】

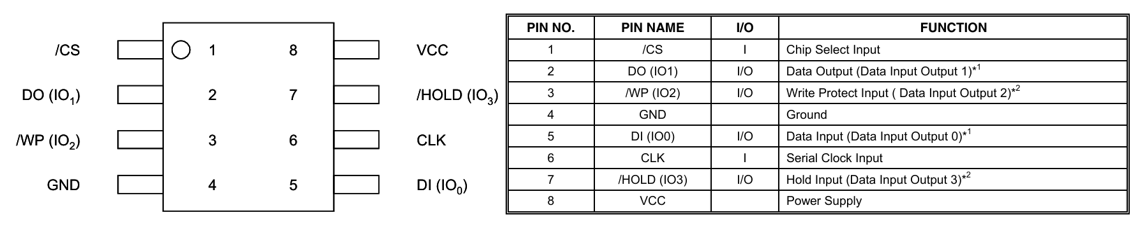

板载Flash芯片型号:W25Q16BV;总容量为16M bit,即2M字节;存储阵列被分成8192个可编程页,每页容量256字节;支持Standard SPI、Dual SPI和Quad SPI三种SPI通信协议,最大读/写传输速率达50MB/s。它支持多种擦除操作,包括扇|贝英语区擦除(4KB)、块擦除(32KB或64KB)以及全芯片擦除。

1、接口处理与结构逻辑

上图可以看到,除SPI经典的四个引脚外,还有/WP和/HOLD,分别用于写保护和输入保持。对于不同倍率SPI协议,引脚使用搭配是有区别的。

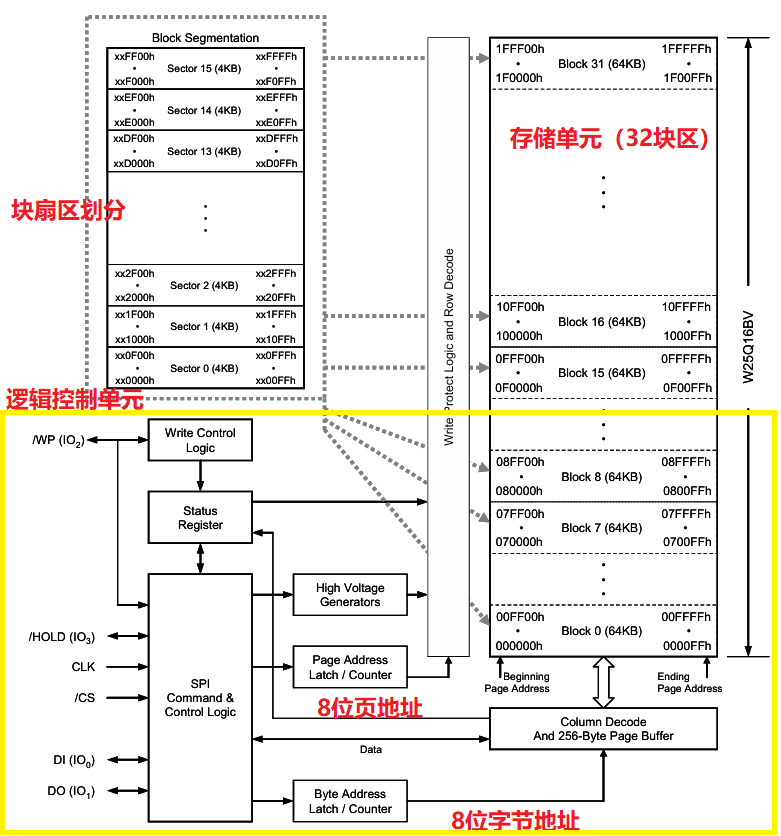

W25Q16BV内部存储结构的逻辑和功能组织见下图,SPI接口负责接收命令和地址,并通过控制逻辑进行解析和执行。状态寄存器(Status Register)用于存储设备的状态信息,如是否忙碌(BUSY位);写控制通过IO2引脚控制,用于启动写操作;高电平生成器(High Voltage Generators)用于执行如擦除等操作;控制逻辑(Control Logic)负责解析SPI接口接收到的命令,并根据需要控制存储器的读/写操作。列解码(Column Decode)和页面缓冲(256-Byte Page Buffer)用于支持页面的读/写操作。

存储器部分被分割成32个块(Block),单个块区包含16个扇区(Sector),每个扇区又由16个页组成,单页存储256字节数据,共计32 x 16 x 16 x 256 ≈ 2M 字节。存储器通过页地址和字节地址来定位特定的数据位置。

24位地址线通过上述的层次结构来映射整个存储器的地址空间,具体见下面表格。

| 分区 | 地址位 |

|---|---|

| 块(Block)地址 | 23~16位(0x1F0000到0x1FFFFF) |

| 扇区(Sector)地址 | 15~12位(0x00F000到0x00FFFF) |

| 页(Page)地址 | 11~8位 |

| 字节(Byte)地址 | 7~0位 |

2、指令与时序说明

软件命令: W25Q16BV的指令集由30条基本指令组成,指令完全通过SPI总线控制。指令的启动是通过/CS的下降边缘来触发的,/CS拉高前须完成指令输入,否则无效。DI输入的第一个字节提供指令代码,DI输入上的数据是在时钟的上升沿采样的,首先采样的是最高有效位(MSB)。指令的长度从单个字节到几个字节不等,后面可能跟着地址字节、数据字节、虚拟字节(可选),在某些情况下,还可能是它们组合。所有的读指令都可以在任何一个时钟位之后完成。

| 指令 | 编码 | 指令 | 编码 |

|---|---|---|---|

| Write Enable | 06h | Write Disable | 04h |

| Sector Erase (4KB) | 20h | Block Erase (32KB) | 52h |

| Block Erase (64KB) | D8h | Chip Erase | C7h/60h |

| Continuous Read Mode Reset | FFh | Read Data | 03h |

| Fast Read | 0Bh | Write Status Register | 01h |

所有写、编程或擦除指令必须在字节边界上完成(即,在完整的8位数据被时钟同步后,/CS被驱动为高)。如果不在字节边界上完成,该指令将被终止。这一特性旨在保护设备免受意外写入的影响。

当内存正在被编程或擦除,或者当状态寄存器正在被写入时,除了读状态寄存器指令之外的所有指令都将被忽略,直到编程或擦除周期完成。

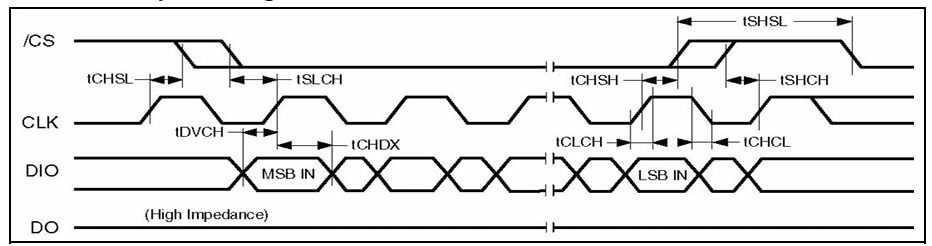

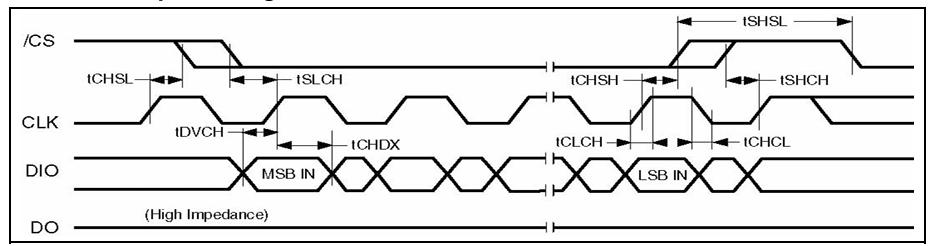

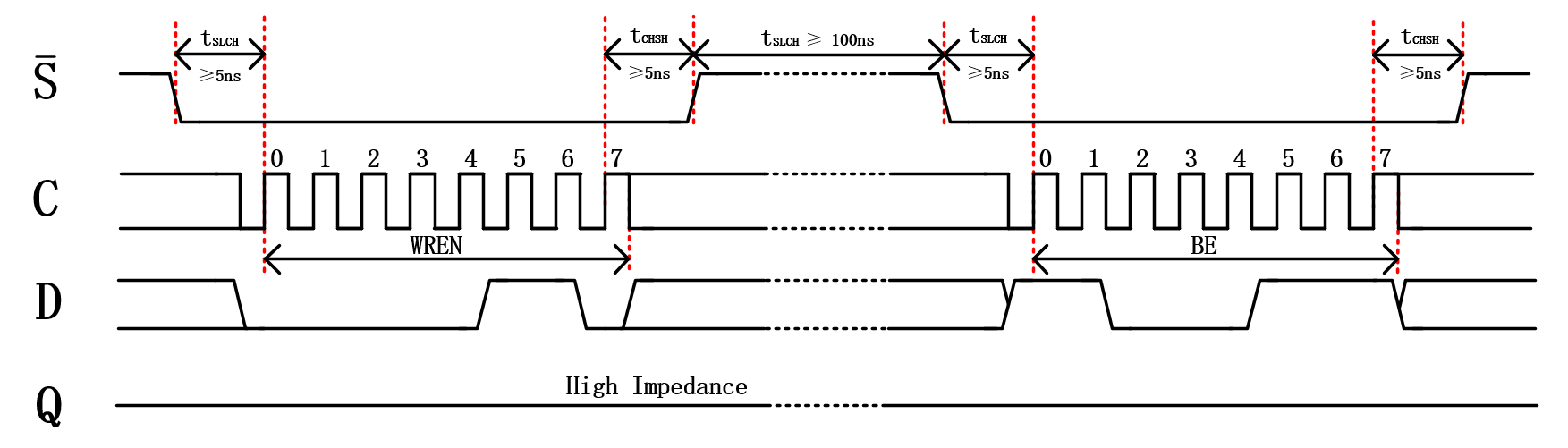

电平切换时序要求:

下图为Serial Input Timing,其中片选线/CS待输入完成后拉高电平保持时间(tSHSL) (for Array Read Array Read / Erase or Program Read Status Registers) :至少7/40 ns;片选信号有效建立时间(tSLCH):至少为5ns;片选信号有效保持时间(tCHSH):至少为5ns。注意:读指令/写指令时钟频率最大为

50Mhz

。

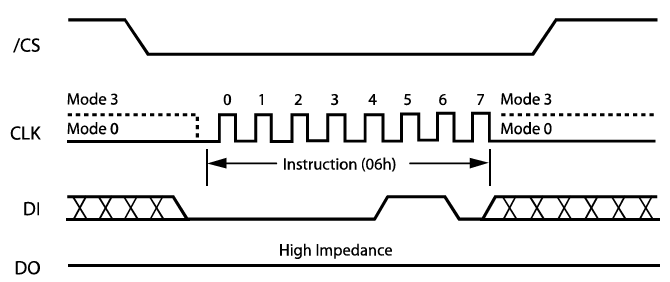

写使能(Write Enable ): 该指令用于设置(状态寄存器中)写使能锁存器(WEL)位为1,确保存储器处于可写状态。

首先,将/CS(Chip Select)引脚拉低,SPI通信启动。在CLK上升沿,将数据输入(DI)引脚上的数据位设置为指令代码“06h”,即0000 0110。完成后,将/CS引脚拉高,SPI通信的结束和写使能完成。

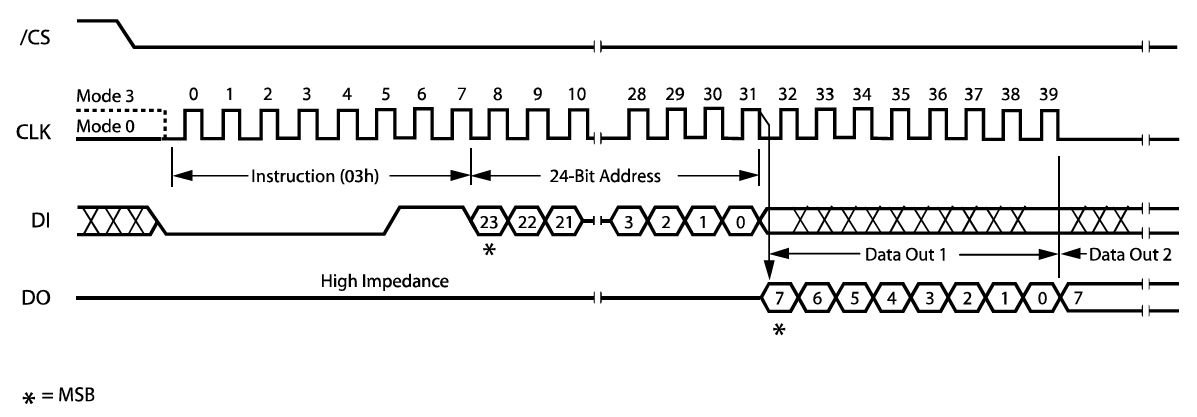

读操作(Read Data): 这个指令允许从存储器中顺序地读取一个或多个数据字节。首先,通过将/CS引脚拉低来启动指令,将指令代码“03h”(0000 0011)和一个24位地址(A23-A0)通过DI引脚移位输入,代码和地址位在CLK上升沿时被锁定。最后,通过将/CS引脚拉高完成指令。

如果在擦除、编程或写入周期正在进行时(BUSY=1)发出读取数据指令,该指令将被忽略。

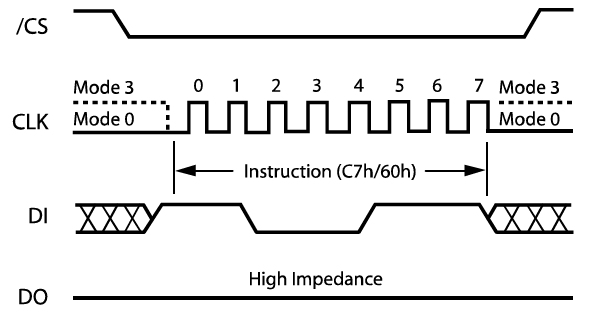

芯片全擦除操作(Chip Erase): Chip Erase 指令会将设备内的所有存储器设置为擦除状态,即所有位都设为1。

①擦除启动: 在执行芯片擦除指令之前,必须先执行一个“写使能”指令,使设备能够接受芯片擦除指令(状态寄存器的WEL位必须等于1)。将/CS引脚拉低来启动指令,移位输入指令代码“C7h”或“60h”,在第八位被锁定后,/CS引脚须被拉高。

②擦除过程: /CS被拉高后,自计时的芯片擦除指令将开始执行。芯片擦除周期(典型3s,最大10s)进行期间,仍然可以通过“读取状态寄存器”指令来检查BUSY位的状态(BUSY位在芯片擦除周期期间为1)。

③擦除后的状态: WEL位会被置0,注意:存储数据的任何部分受到块保护(BP2、BP1和BP0)位的保护,则不会执行芯片擦除指令。

【Flash全擦除操作】

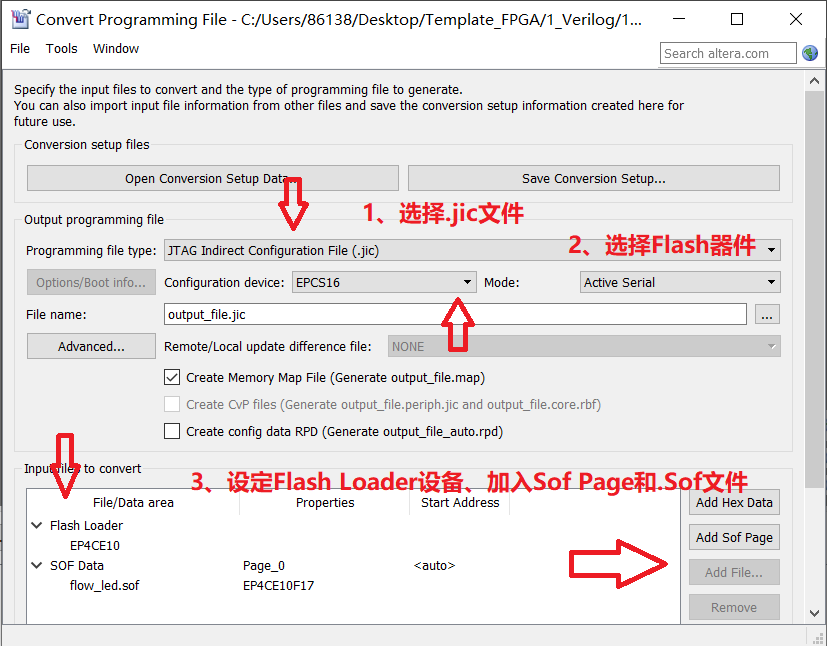

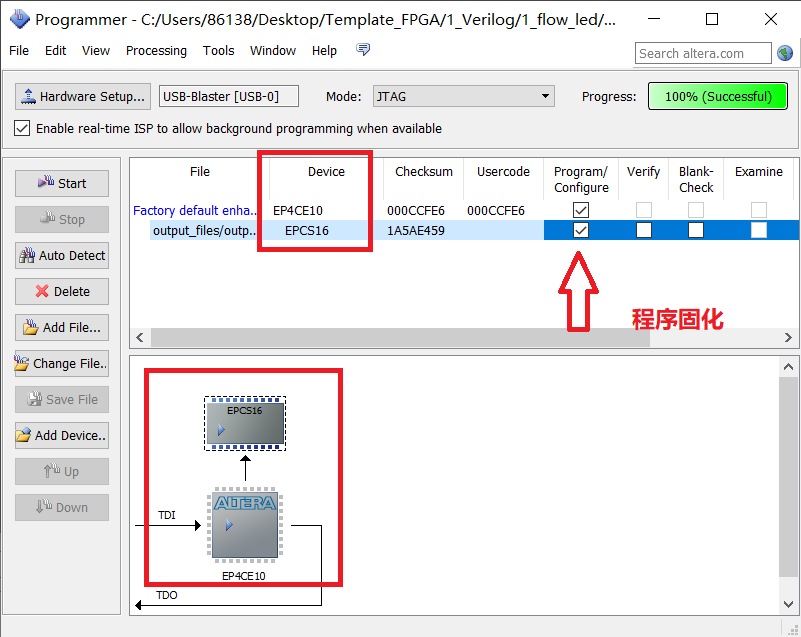

1、Quartus II进行程序固化下载及擦除

烧录程序方式: ①将程序下载到FPGA内部的SRAM之中,烧录过程耗时较短,但掉电后程序丢失;②将程序固化到FPGA外部挂载的非易失性存储器Flash芯片,掉电后程序不丢失。

在Quartus II的主界面中,选择“File”菜单下的“Convert Programming Files”选项,用于将编译生成的特定文件(如sof文件)转换为其他格式的文件,如jic文件,以便下载到FPGA板载的flash或其他目标设备中,流程见下图。

下载程序时,目标.jic文件后,右下指示框很明显看到下载至Flash(这里是EPCS16类似W25Q16),仅勾选Program/Configure 进行程序固化下载,仅勾选Erase表示擦除Flash操作。

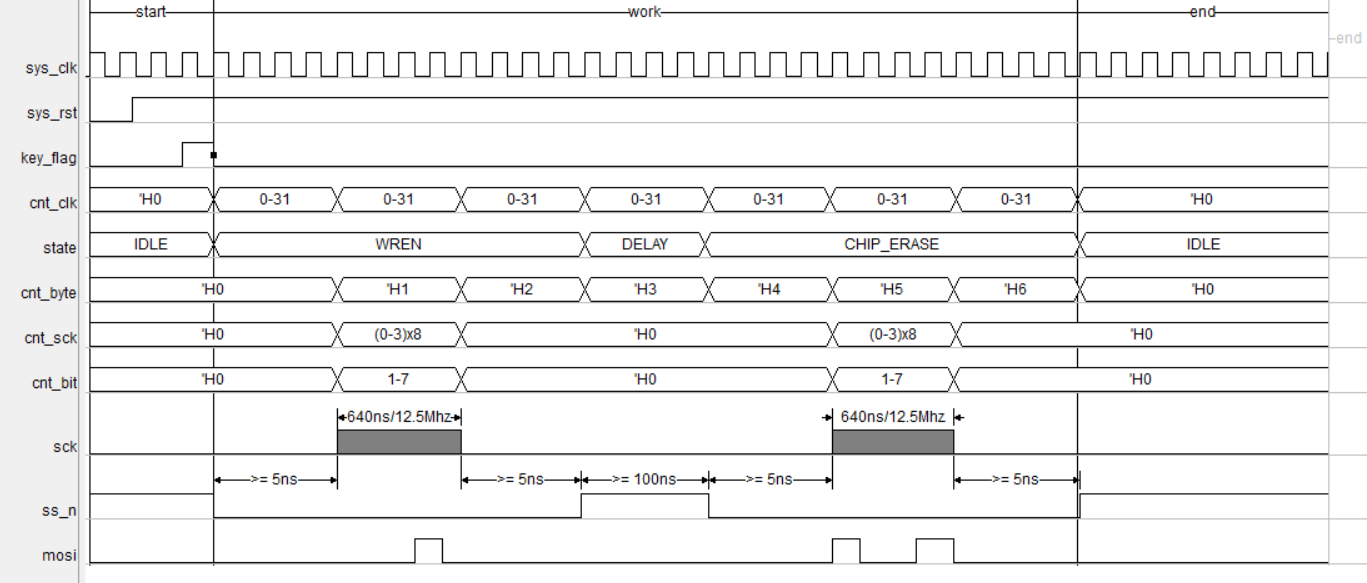

2、Verilog程序实现Flash芯片擦除操作(SPI)

根据Flash读/写时序要求,片选信号拉低后,需进行5ns(tSLCH≥5ns)等待时间,及后写入写使能指令。写入完成后,再次进行5ns(tCHSH≥5ns)等待,拉高片选线维持≥100ns,接续完成写入操作指令流程。

Flash芯片数据读操作的时钟频率(SCK)上限为50MHz,这里通过四分频设定SCK频率为12.5Mhz。单个时钟周期写入1 bit数据,完整的单字节指令需要8个完整的SCK时钟周期,即32个完整的系统时钟,系统时钟频率为50MHz,完整指令的写入需要640ns。

mosi

信号输出采用了状态机转移的逻辑方法:

| 状态 | 说明 | 状态 | 说明 |

|---|---|---|---|

IDLE

|

空闲初始状态,等待触发信号 |

WR_EN

|

发送写使能指令 |

DELAY

|

等待状态,保持时序 |

CH_ER

|

芯片擦除指令发送 |

当

key_Flag

信号有效时,从

IDLE

转移到

WR_EN

状态,在

WR_EN

和

CH_ER

状态中,分别写入相应的写使能和指令后,等待

tCHSH

时间,然后拉高片选信号。在

WR_EN

状态写入指令后,转移到

DELAY

状态等待

tSHSL

时间。在

DELAY

状态等待完成后,转移到

CH_ER

状态,返回

IDLE

状态。相关代码如下:

parameter IDLE = 4'b0001, WREN = 4'b0010, DELAY= 4'b0100, CH_ER= 4'b1000;

parameter WREN_CODE = 8'b0000_0110, CH_ER_CODE = 8'b1100_0111;

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) state <= IDLE;

else case(state)

IDLE :if(key_flag)state <= WREN;

WREN :if((cnt_byte == 3'd2)&&(cnt_clk == 5'd31))state <= DELAY;

DELAY:if((cnt_byte == 3'd3)&&(cnt_clk == 5'd31))state <= CH_ER;

CH_ER:if((cnt_byte == 3'd6)&&(cnt_clk == 5'd31))state <= IDLE;

default:state <= IDLE;

endcase

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) mosi <= 1'b0;

else if((state == WREN)&&(cnt_byte == 3'd2)) mosi <= 1'b0;

else if((state == CH_ER)&&(cnt_byte == 3'd6)) mosi <= 1'b0;

else if((state == WREN)&&(cnt_byte == 3'd1)&&(cnt_sck == 2'd0))

mosi <= WREN_CODE[7 - cnt_bit];

else if((state == CH_ER) && (cnt_byte == 3'd5) && (cnt_sck == 2'd0))

mosi <= CH_ER_CODE[7 - cnt_bit];

end

而对于其他的信号逻辑处理:

cnt_clk

作为预期设定单位间距(640ns)的计数器,

cnt_byte

根据其完成7个阶段的转换。

sck

为写操作的时钟信号,

cnt_sck

作为其在有效时间段内计数器,使得

sck

按

sys_clk

四分配输出。

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) cnt_clk <= 5'd0;

else if(state != IDLE) cnt_clk <= cnt_clk + 1'b1; //位宽清零

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) cnt_byte <= 3'd0;

else if((cnt_byte == 3'd6)&&(cnt_clk == 5'd31)) cnt_byte <= 3'd0;

else if(cnt_clk == 5'd31) cnt_byte <= cnt_byte + 1'b1;

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) cnt_sck <= 2'd0;

else if((state == WREN)&&(cnt_byte == 3'd1)) cnt_sck <= cnt_sck + 1'b1; //位宽清零

else if((state == CH_ER)&&(cnt_byte == 3'd5)) cnt_sck <= cnt_sck + 1'b1; //位宽清零

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) cnt_bit <= 3'd0;

else if(cnt_sck == 2'd2) cnt_bit <= cnt_bit + 1'b1;

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) ss_n <= 1'b1;

else if(key_flag) ss_n <= 1'b0;

else if((cnt_byte == 3'd2)&&(cnt_clk == 5'd31)&&(state == WREN)) ss_n <= 1'b1;

else if((cnt_byte == 3'd3)&&(cnt_clk == 5'd31)&&(state == DELAY)) ss_n <= 1'b0;

else if((cnt_byte == 3'd6)&&(cnt_clk == 5'd31)&&(state == CH_ER)) ss_n <= 1'b1;

end

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst) sck <= 1'b0;

else if(cnt_sck == 2'd0) sck <= 1'b0;

else if(cnt_sck == 2'd2) sck <= 1'b1;

end

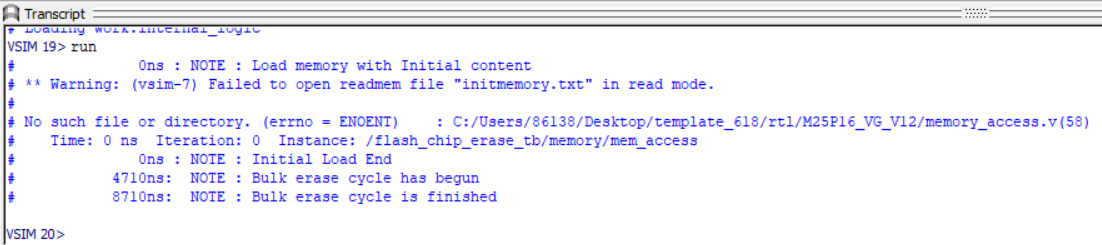

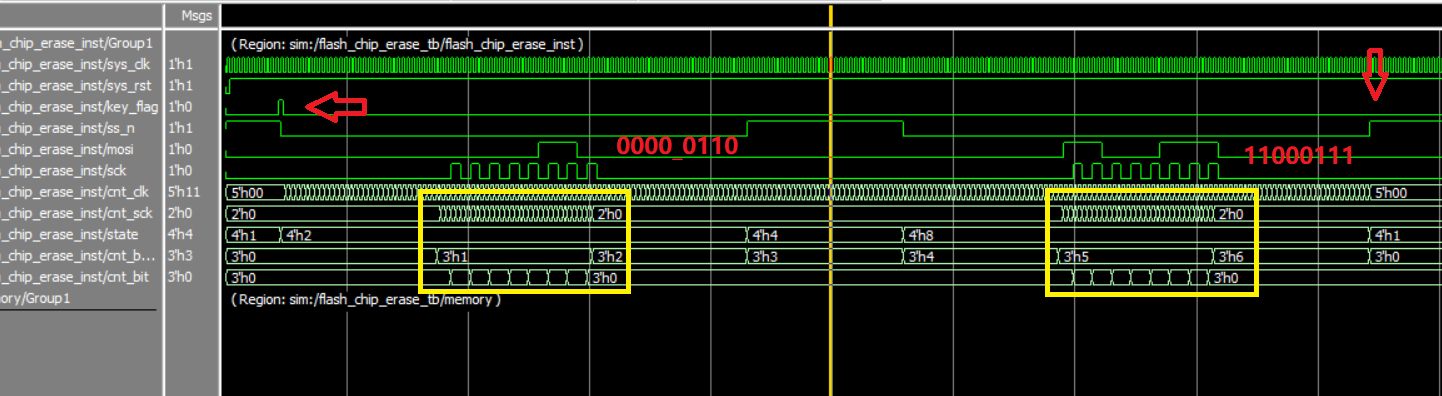

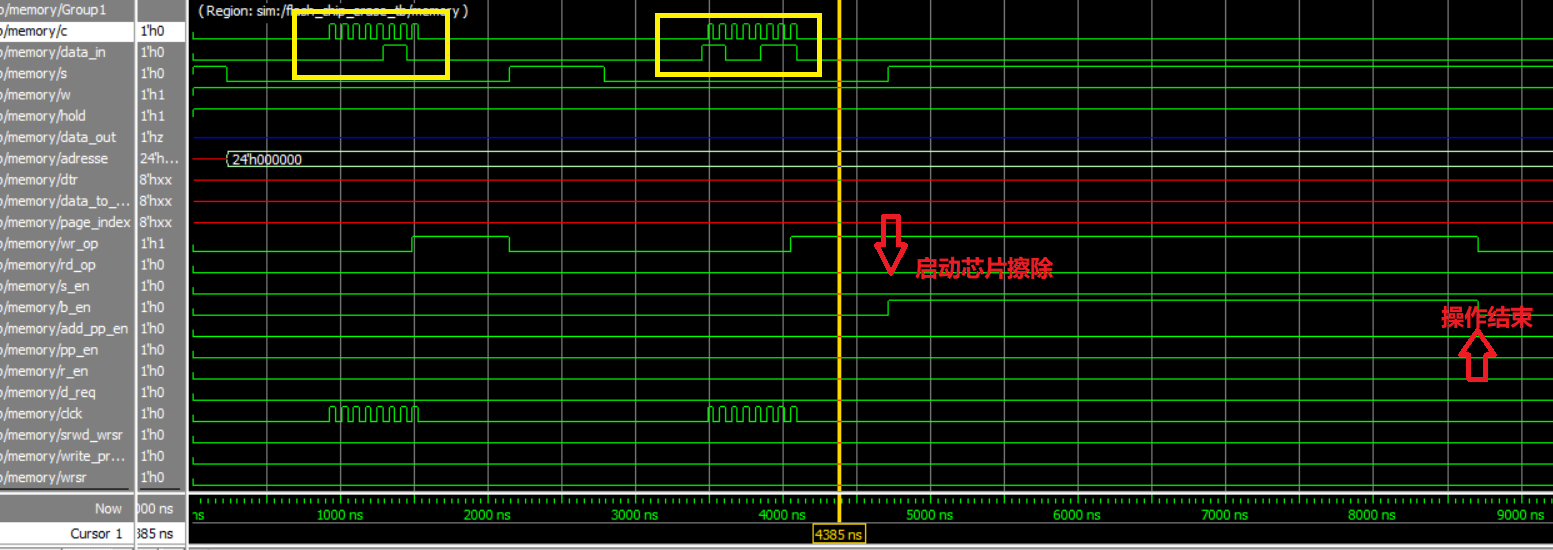

导入仿真文件,对芯片擦除操作进行仿真,由于该操作耗时长,仿真前在Flash参数文件缩放擦除周期至4000ns。从上图仿真结果可以看到,在4710ns处,Flash启动芯片擦除,在8710ns结束擦除操作。

根据仿真结果显示,

sys_clk

拉高后,程序正常工作,当检测到

key_flag

为高电平后,片选线

SS_n

拉低,指令操作开启。等待一个有效建立时间后(这里是640ns,便于编写代码),

sck

正式输出八段时钟切换(12.5Mhz)。首先,按写使能指令,输出一个时序(0000_0110,06h)。等待一个片选线建立时间后拉高,进入等待状态(≥100ns,640ns)接续完成芯片擦除指令的录入。

cnt_byte

和

state

的状态,随

cnt_clk

时钟计数变换。

文献参考:

[1]刘满. SPI协议接口的设计与实现[D]. 陕西:西安电子科技大学,2020;

[2]基于spi协议的flash驱动控制( https://doc.embedfire.com/fpga/altera/ep4ce10_pro/zh/latest/code/spi_flash.html );

[3] W25Q16BV Datasheet(PDF) - Winbond (alldatasheet.com) ;

本篇文章中使用的Verilog程序模块,若有需见网页左栏Gitee仓库链接: https://gitee.com/silly-big-head/little-mouse-Funnyhouse/tree/FPGA-Verilog/

浪漫庄园OPPO版下载 v2.0.5 安卓版

浪漫庄园OPPO版下载 v2.0.5 安卓版 仙山小农 官方下载

仙山小农 官方下载 修狗逃生 官方正版

修狗逃生 官方正版 帝国文明2 决定版

帝国文明2 决定版 服装店模拟器

服装店模拟器 托卡小厨房2中文版

托卡小厨房2中文版 云浅攻速大极品

云浅攻速大极品 砍怪爆爽透视超变

砍怪爆爽透视超变 快乐方块屋安卓版

快乐方块屋安卓版 节奏盒子畸形动物园模组手机版

节奏盒子畸形动物园模组手机版 糯米传奇

糯米传奇 囚禁之馆 官方中文版

囚禁之馆 官方中文版 nba 2k20 官网版

nba 2k20 官网版 剑侠世界起源充值折扣平台版下载 v1.15.26 安卓版

剑侠世界起源充值折扣平台版下载 v1.15.26 安卓版

- Canvas在前端开发中的重要性和应用

- Java IO流中的数据流分类

- 自定义实现H5页面下拉刷新功能

- 高级前端开发需要知道的 25 个 JavaScript 单行代码

- MyBatis 的缓存机制

- 解决Docker镜像下载问题的Java工具

- Lakehouse 还是 Warehouse?(2/2).md

- C#进程调用FFmpeg操作音视频

- TiKV 源码分析之 PointGet

- 讯飞有一个可以根据描述文本自动生成PPT的AI接口,有趣

- 解决el-upload上传多张图片报错ERR_UPLOAD_FILE_CHANGED的问题

- 从零开始写 Docker(十八)---容器网络实现(下):为容器插上”网线“

- 1

加查之花 正版

- 2

爪女孩 最新版

- 3

企鹅岛 官方正版中文版

- 4

捕鱼大世界 无限金币版

- 5

情商天花板 2024最新版

- 6

内蒙打大a真人版

- 7

烦人的村民 手机版

- 8

跳跃之王手游

- 9

球球英雄 手游

- 10

蛋仔派对 国服版本

加查之花 正版

加查之花 正版 爪女孩 最新版

爪女孩 最新版 企鹅岛 官方正版中文版

企鹅岛 官方正版中文版 捕鱼大世界 无限金币版

捕鱼大世界 无限金币版 情商天花板 2024最新版

情商天花板 2024最新版 内蒙打大a真人版

内蒙打大a真人版 烦人的村民 手机版

烦人的村民 手机版 跳跃之王手游

跳跃之王手游 球球英雄 手游

球球英雄 手游 蛋仔派对 国服版本

蛋仔派对 国服版本 地铁跑酷忘忧10.0原神启动 安卓版

地铁跑酷忘忧10.0原神启动 安卓版 芭比公主宠物城堡游戏 1.9 安卓版

芭比公主宠物城堡游戏 1.9 安卓版 挂机小铁匠游戏 122 安卓版

挂机小铁匠游戏 122 安卓版 咸鱼大翻身游戏 1.18397 安卓版

咸鱼大翻身游戏 1.18397 安卓版 死神之影2游戏 0.42.0 安卓版

死神之影2游戏 0.42.0 安卓版 跨越奔跑大师游戏 0.1 安卓版

跨越奔跑大师游戏 0.1 安卓版 灵魂潮汐手游 0.45.3 安卓版

灵魂潮汐手游 0.45.3 安卓版 旋转陀螺多人对战游戏 1.3.1 安卓版

旋转陀螺多人对战游戏 1.3.1 安卓版 地铁跑酷黑白水下城魔改版本 3.9.0 安卓版

地铁跑酷黑白水下城魔改版本 3.9.0 安卓版 Escapist游戏 1.1 安卓版

Escapist游戏 1.1 安卓版